Pencetus ialah elemen teknologi digital, peranti bistable yang beralih ke salah satu keadaan dan boleh kekal di dalamnya selama-lamanya walaupun isyarat luaran dialih keluar. Ia dibina daripada elemen logik tahap pertama (DAN-BUKAN, ATAU-TIDAK, dll.) dan tergolong dalam peranti logik peringkat kedua.

Dalam amalan, flip-flop dihasilkan dalam bentuk litar mikro dalam pakej berasingan atau dimasukkan sebagai elemen dalam litar bersepadu besar (LSI) atau tatasusunan logik boleh atur cara (PLM).

Kandungan

Pengelasan dan jenis penyegerakan pencetus

Pencetus terbahagi kepada dua kelas yang luas:

- tak segerak;

- segerak (berjam).

Perbezaan asas di antara mereka ialah untuk kategori peranti pertama, tahap isyarat keluaran berubah serentak dengan perubahan isyarat pada input (input).Untuk pencetus segerak, perubahan keadaan berlaku hanya jika terdapat isyarat penyegerakan (jam, strob) pada input yang disediakan untuk ini. Untuk ini, output khas disediakan, dilambangkan dengan huruf C (jam). Mengikut jenis gating, elemen segerak dibahagikan kepada dua kelas:

- dinamik;

- statik.

Untuk jenis pertama, tahap output berubah bergantung pada konfigurasi isyarat input pada masa kemunculan hadapan (tepi hadapan) atau kejatuhan nadi jam (bergantung pada jenis pencetus tertentu). Di antara kemunculan bahagian hadapan penyegerakan (cerun), sebarang isyarat boleh digunakan pada input, keadaan pencetus tidak akan berubah. Dalam pilihan kedua, tanda jam bukanlah perubahan dalam tahap, tetapi kehadiran satu atau sifar pada input Jam. Terdapat juga peranti pencetus kompleks yang dikelaskan mengikut:

- bilangan keadaan stabil (3 atau lebih, berbeza dengan 2 untuk elemen utama);

- bilangan peringkat (juga lebih daripada 3);

- ciri-ciri lain.

Elemen kompleks adalah penggunaan terhad dalam peranti tertentu.

Jenis pencetus dan cara ia berfungsi

Terdapat beberapa jenis pencetus asas. Sebelum memahami perbezaan, sifat biasa harus diperhatikan: apabila kuasa digunakan, output mana-mana peranti ditetapkan kepada keadaan sewenang-wenangnya. Jika ini penting untuk operasi keseluruhan litar, litar pratetap mesti disediakan. Dalam kes yang paling mudah, ini adalah litar RC yang menghasilkan isyarat untuk menetapkan keadaan awal.

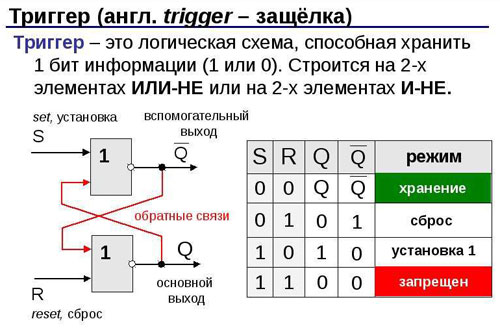

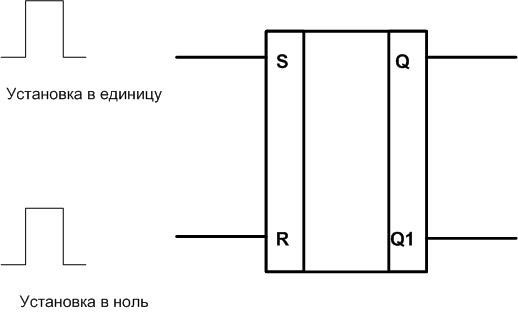

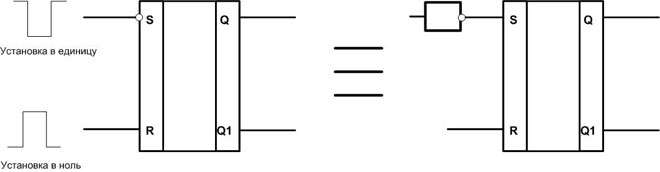

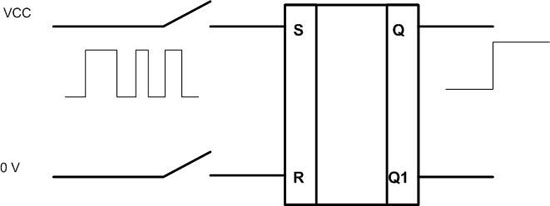

RS selipar

Jenis peranti bistable tak segerak yang paling biasa ialah flip-flop RS. Ia merujuk kepada flip-flop dengan tetapan keadaan 0 dan 1 yang berasingan.Terdapat dua input untuk ini:

- S - set (pemasangan);

- R - set semula (set semula).

Terdapat keluaran langsung Q, terdapat juga keluaran terbalik Q1. Tahap logik padanya sentiasa bertentangan dengan tahap pada Q - ini berguna apabila mereka bentuk litar.

Apabila tahap positif digunakan pada input S, output Q akan ditetapkan kepada unit logik (jika terdapat output terbalik, ia akan pergi ke tahap 0). Selepas itu, pada input persediaan, isyarat boleh berubah mengikut kehendak anda - ini tidak akan menjejaskan tahap output. Sehingga 1 muncul pada input R. Ini akan menetapkan flip-flop kepada keadaan 0 (1 pada output terbalik). Sekarang menukar isyarat pada input tetapan semula tidak akan menjejaskan keadaan elemen selanjutnya.

Penting! Pilihan apabila terdapat unit logik pada kedua-dua input adalah dilarang. Pencetus akan ditetapkan kepada keadaan sewenang-wenangnya. Apabila mereka bentuk skema, keadaan ini harus dielakkan.

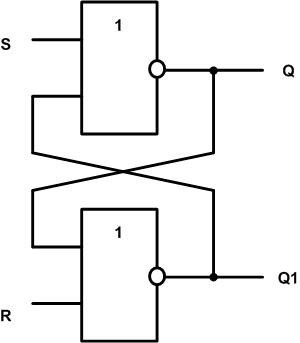

Flip-flop RS boleh dibina berdasarkan elemen NAND dua input yang digunakan secara meluas. Kaedah ini dilaksanakan pada kedua-dua litar mikro konvensional dan dalam matriks boleh atur cara.

Satu atau kedua-dua input boleh diterbalikkan. Ini bermakna bahawa pada pin ini, pencetus dikawal oleh penampilan bukan tahap tinggi, tetapi tahap rendah.

Jika anda membina flip-flop RS pada elemen dua input DAN-BUKAN, maka kedua-dua input akan songsang - dikawal oleh bekalan sifar logik.

Terdapat versi berpagar flip-flop RS. Ia mempunyai input tambahan C. Penukaran berlaku apabila dua syarat dipenuhi:

- kehadiran tahap tinggi pada input Set atau Set Semula;

- kehadiran isyarat jam.

Elemen sedemikian digunakan dalam kes di mana pensuisan mesti ditangguhkan, sebagai contoh, pada masa penghujung transien.

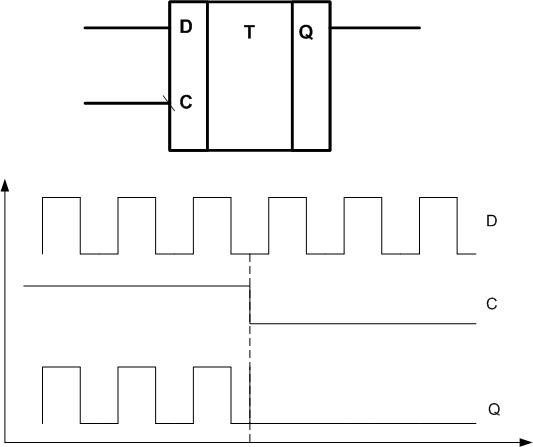

D selipar

Pencetus D ("pencetus lutsinar", "selak", selak) tergolong dalam kategori peranti segerak, dijam oleh input C. Terdapat juga input data D (Data). Dari segi kefungsian, peranti itu tergolong dalam pencetus dengan penerimaan maklumat melalui satu input.

Selagi yang logik hadir pada input jam, isyarat pada output Q mengulangi isyarat pada input data (mod ketelusan). Sebaik sahaja tahap strob pergi ke keadaan 0, tahap pada output Q akan kekal sama seperti pada masa tepi (selak). Jadi anda boleh menetapkan tahap input pada input pada bila-bila masa. Terdapat juga D-flip-flop dengan jam di hadapan. Mereka menyelak isyarat pada tepi positif strob.

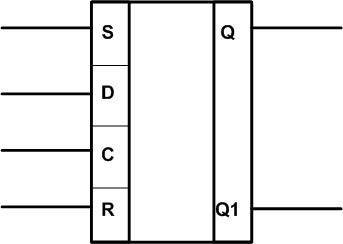

Dalam amalan, dua jenis peranti bistable boleh digabungkan dalam satu litar mikro. Contohnya, D dan RS flip-flop. Dalam kes ini, input Set/Reset mempunyai keutamaan. Jika terdapat sifar logik pada mereka, maka elemen itu berkelakuan seperti D-flip-flop biasa. Apabila tahap tinggi berlaku sekurang-kurangnya satu input, output ditetapkan kepada 0 atau 1, tanpa mengira isyarat pada input C dan D.

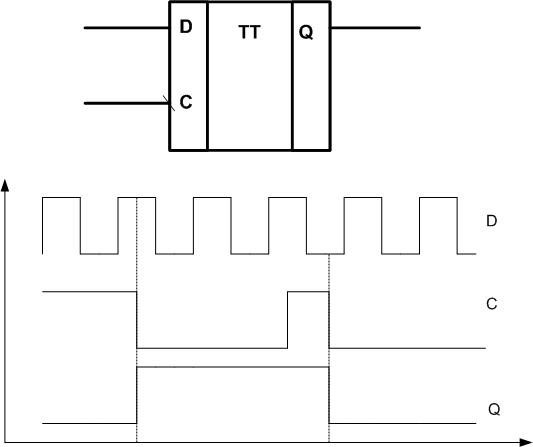

Ketelusan flip-flop D tidak selalunya merupakan ciri yang berguna. Untuk mengelakkannya, elemen berganda digunakan (flip-flop, pencetus "bertepuk tangan"), ia dilambangkan dengan huruf TT. Pencetus pertama ialah selak biasa yang menghantar isyarat input ke output. Pencetus kedua berfungsi sebagai elemen ingatan. Kedua-dua peranti jam dengan satu strob.

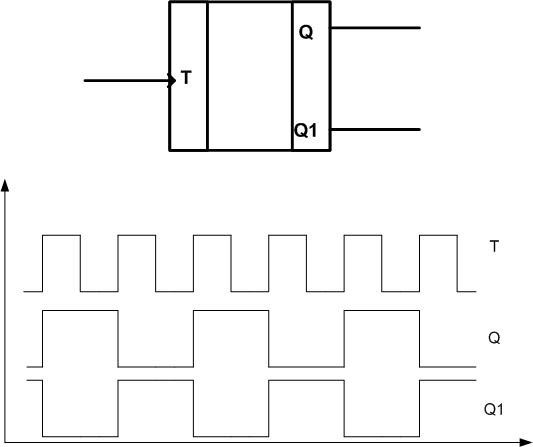

T-flip-flop

Pencetus-T tergolong dalam kelas unsur bistable boleh dikira. Logik kerjanya adalah mudah - ia menukar keadaannya setiap kali apabila unit logik seterusnya datang ke inputnya.Jika isyarat nadi digunakan pada input, frekuensi output akan menjadi dua kali lebih tinggi daripada input. Pada output terbalik, isyarat akan keluar dari fasa dengan yang langsung.

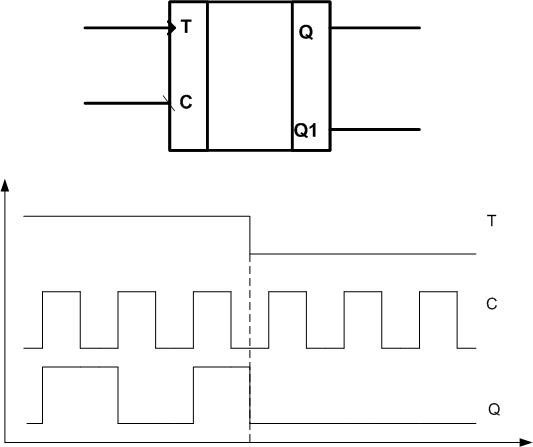

Beginilah cara T-flip-flop tak segerak berfungsi. Terdapat juga pilihan segerak. Apabila isyarat nadi digunakan pada input jam dan dengan kehadiran unit logik pada output T, elemen berkelakuan dengan cara yang sama seperti yang tidak segerak - ia membahagikan frekuensi input kepada separuh. Jika pin T adalah logik sifar, maka output Q ditetapkan rendah, tanpa mengira kehadiran strob.

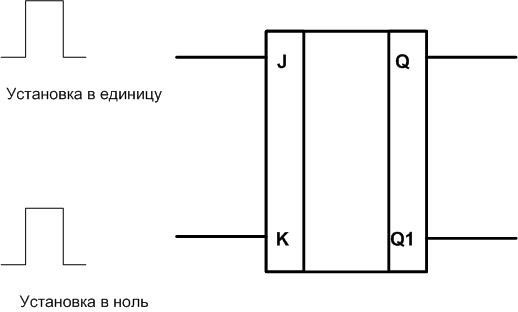

JK selipar

JK selipar

Unsur bistable ini tergolong dalam kategori yang universal. Ia boleh dikawal secara berasingan oleh input. Logik flip-flop JK adalah serupa dengan kerja elemen RS. Input J (Job) digunakan untuk menetapkan output kepada satu. Tahap tinggi pada pin K (Keep) menetapkan semula output kepada sifar. Perbezaan asas daripada pencetus RS ialah penampilan serentak yang pada dua input kawalan tidak dilarang. Dalam kes ini, keluaran elemen mengubah keadaannya kepada sebaliknya.

Jika output Job dan Keep disambungkan, maka JK-flip-flop bertukar menjadi T-flip-flop pengiraan tak segerak. Apabila gelombang persegi digunakan pada input gabungan, output akan menjadi separuh frekuensi. Seperti elemen RS, terdapat versi jam flip-flop JK. Dalam amalan, ia adalah terutamanya elemen berpagar jenis ini yang digunakan.

Penggunaan praktikal

Sifat pencetus untuk mengekalkan maklumat yang direkodkan walaupun isyarat luaran dialih keluar membolehkannya digunakan sebagai sel memori dengan kapasiti 1 bit.Daripada elemen tunggal, anda boleh membina matriks untuk menyimpan keadaan binari - mengikut prinsip ini, kenangan capaian rawak statik (SRAM) dibina. Ciri ingatan sedemikian ialah litar mudah yang tidak memerlukan pengawal tambahan. Oleh itu, SRAM tersebut digunakan dalam pengawal dan PLA. Tetapi ketumpatan rakaman yang rendah menghalang penggunaan matriks sedemikian dalam PC dan sistem pengkomputeran berkuasa lain.

Penggunaan flip-flop sebagai pembahagi frekuensi telah disebutkan di atas. Unsur bistable boleh disambungkan dalam rantai dan mendapatkan nisbah pembahagian yang berbeza. Rentetan yang sama boleh digunakan sebagai pembilang nadi. Untuk melakukan ini, adalah perlu untuk membaca keadaan output dari elemen perantaraan pada setiap saat masa - kod binari akan diperoleh bersamaan dengan bilangan denyutan yang datang ke input elemen pertama.

Bergantung pada jenis pencetus yang digunakan, pembilang boleh menjadi segerak atau tak segerak. Penukar bersiri kepada selari dibina berdasarkan prinsip yang sama, tetapi hanya elemen berpagar digunakan di sini. Juga, talian kelewatan digital dan elemen lain teknologi binari dibina di atas pencetus.

Selipar RS digunakan sebagai pengapit aras (penekan lantunan). Jika suis mekanikal (butang, suis) digunakan sebagai sumber aras logik, maka apabila ditekan, kesan lantunan akan membentuk banyak isyarat dan bukannya satu. RS flip-flop berjaya melawan ini.

Skop peranti bistable adalah luas. Pelbagai tugas yang diselesaikan dengan bantuan mereka sebahagian besarnya bergantung pada imaginasi pereka, terutamanya dalam bidang penyelesaian bukan standard.

Artikel yang serupa: